# Compact Switched Capacitor Multilevel Inverter (CSCMLI) With Self Voltage Balancing and Boosting Ability

M. Jagabar Sathik, Member, IEEE and K.Vijayakumar, Senior Member, IEEE

Abstract: - This letter presents a compact switched capacitor multilevel inverter topology with reduced switch count and with self-voltage balancing and boosting ability. The operational mode of proposed CSCMLI is discussed. A comparative analysis in terms of number of switches and blocking voltages is presented against recent switched capacitor multilevel inverter topologies. Further to enhance the quality of the output voltage, a new level shifted multicarrier PWM modulation technique is recommended. This modulation technique produces low THD and high rms voltage. The proposed modulation technique is implemented in the nine-level CSCMLI with single dc source and two capacitors. The simulated and experimental results are verified for a switching frequency of 50Hz and 2.5 kHz using the proposed PWM control.

*Index Terms*: cascaded multilevel inverter, single-stage capacitor module, PWM technique, voltage boosting, voltage balancing

#### I. INTRODUCTION

The design of converters for renewable energy system is another challenge for power electronics researchers. The widely installed renewable energy sources such as photovoltaic, wind and fuel cell are highly participating in energy conversion [1]. Multilevel inverters are playing major role in these energy conversion systems. These inverters comprise of dc source, active switches, series of capacitors and power diodes. The conventional multilevel inverters such as neutral point clamped, flying capacitor and cascaded H-bridge are predominantly used in medium to high voltage applications. The cascaded H-bridge topology has unique advantages like modularity and lower number of power components [2-3]. Even though, the conventional topologies have more features like modularity and low dv/dt stress, it suffers from the use of more number of active and passive devices and also balancing of capacitor voltages are still challenging. To minimize the drawbacks of conventional topologies, recent multilevel inverters are presented in [4]-[11]. The objectives of these topologies are to minimize the number of dc source, active switches and self-balancing of capacitor voltages. The high frequency cascaded inverter for grid connected PV and electric vehicle is proposed with reduced switching frequency in [4]. Each unit consists of six active switches, a diode, a dc source and a capacitor. The capacitor charging and discharging is done through proper switching sequence with single source to generate five level stepped output voltage. The reduced switch count with self-voltage balancing of series and parallel connection of capacitor is presented in [5]. The fundamental and high frequency modulation technique for the proposed topology is compared in terms of power losses.

A new voltage step-up structure with self-balancing is discussed in [6]. The capacitors are charged in first two states and discharged in the next two states to produce the nine-level output voltage. To increase the level, the series connection of

basic unit is also recommended. Another high step up voltage inverter with reduced switches and self-voltage balancing is presented in [7]. The proposed basic cell comprises of a capacitor, a diode and two switches. In each cycle, the series and/or parallel connection of capacitors are charged and discharged. However, the topology presented in [5]-[7] uses full bridge inverter as a second stage of conversion which has to block the high voltage, because it increases the *dv/dt* stress on the switches.

To minimize this dv/dt stresses without losing the other features of above inverters, the new multilevel inverters structures are presented in [8]-[11]. In [8], the single dc source without full bridge inverter is presented. This topology has lower dv/dt stress on individual switch, but the number of capacitors and active switches are increasing as the number of level increases. Hybrid switched capacitor inverter for two symmetric and asymmetric configurations are demonstrated in [9]-[10]. One switch & diode in each full bridge unit is added to charge the capacitor, but the number of switches are high as number of level increases. The single stage switched capacitor  $(S^3CM)$  module is demonstrated in [11] which is the modified version of topology presented in [6]. The main objective of  $S^3CM$  topology is to minimize the blocking voltage across the switches and it uses single dc source as the input, but the switch count is high.

To resolve the drawbacks of  $S^3CM$ , this letter presents a compact switched capacitor multilevel inverter (CSCMLI) topology with self-voltage balancing and boosting ability with reduced number of switches. The balancing of the voltages across the capacitors are achieved by choosing proper switching sequence to charge and discharge the capacitor. The capacitors are integrated to maintain the equal average voltage during the switching operation. Further to enhance the quality of output voltage, a new level shifted multicarrier PWM modulation scheme is presented. The features of proposed topology and modulation schemes are:

- 1) Total number of power components are reduced.

- 2) The maximum blocking voltage on individual switches is limited to  $V_{in}$ .

- 3) Due to less number of components, it reduces the number of on-state switches and power losses.

- 4) The voltages across the capacitors are self-balanced and the capacitor voltages  $(C_1 \& C_2)$  are independent of the load power factor.

- 5) The modulation scheme generates low harmonics and high RMS voltage compared to conventional PWM technique. This letter is organized as follows: section II presents the construction of the proposed 9-level inverter with simple explanation on the various modes of operation with new modulation scheme and the generalized Fourier analysis. In Section III, the simulation and experimental results are discussed and section IV, brief the conclusion.

- II. OPERATION OF PROPOSED CSCMLI TOPOLOGY

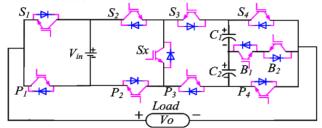

The single phase circuit diagram of the proposed CSCMLI topology is depicted in Fig.1.It constitutes of single input dc source, two series connected dc-link capacitor, and eleven switches (IGBTs). The CSCMLI topology is able to generate a maximum of nine-level stepped voltage, but the number of output voltage can be extended to "m" level by cascading the basic unit of CSCMLI.

Fig.1 Proposed capacitor switched-9-level inverter module

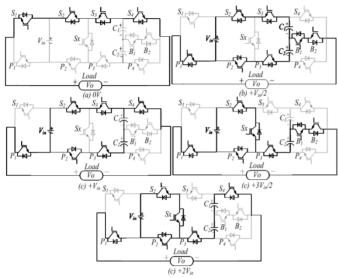

Fig.2(a)-(e) Mode operation for zero state and positive half cycle

TABLE.1 SWITCHING SEQUENCE OF EACH LEVEL FOR OUTPUT VOLTAGE WITH STATE OF CAPACITORS

| State | On-State Switches                                                                                              | Output<br>Voltage | State<br>Capacitors |          |

|-------|----------------------------------------------------------------------------------------------------------------|-------------------|---------------------|----------|

|       |                                                                                                                | $(V_o)$           | $V_{C1}$            | $V_{C2}$ |

| 0     | $S_1,S_2,S_3,S_4/P_1,P_2,P_3P_4$                                                                               | 0V                | -                   | -        |

| 1     | $S_2,S_3,P_3,P_4,B_1,B_2$                                                                                      | C                 | C                   |          |

|       | S <sub>1</sub> ,S <sub>2</sub> ,S <sub>3</sub> ,P <sub>2</sub> ,P <sub>3</sub> ,B <sub>1</sub> ,B <sub>2</sub> |                   |                     |          |

| 2     | $S_2,S_3,S_4,P_1,P_2,P_3$                                                                                      | $+ V_{in}$        |                     |          |

| 2     | $S_1, S_2, S_3, P_2, P_3, P_4$                                                                                 | - V <sub>in</sub> |                     |          |

| 3     | $S_2,P_1,P_3,S_x,B_1,B_2$                                                                                      | $+3V_{in}/2$      |                     |          |

| 3     | $S_1, S_3, P_2, S_x, B_1, B_2$                                                                                 | D                 | D                   |          |

| 4     | $S_2,S_4,P_1,P_3,S_x$                                                                                          | $+2V_{in}$        | D                   | D        |

|       | $S_1, S_3, P2, P_4, S_x$                                                                                       | $-2V_{in}$        |                     |          |

It is worth mentioning that the CSCMLI requires a maximum voltage rating on switches of  $V_{in}$  for m-level. The  $S_I$ - $S_4$ & $P_I$ - $P_4$ are unidirectional switches with anti-parallel diode whereas the  $B_I$ - $B_2$  combinedly act as bidirectional switch i.e two IGBTs are connected in anti-series to allow the current to flow in both the directions and it has the maximum withstanding voltage of  $0.5V_{in}$ . The switch pairs  $(S_I, P_I)$ ,  $(S_2, P_2, S_x)$ ,  $(S_3, P_3, S_x)$  and  $(S_4, P_4)$  should not be turned on simultaneously to avoid the short circuits of the switches with dc source. The switch  $S_x$  is placed parallel to the dc source which provides the current path to discharge the capacitors in third and fourth state. The circuit

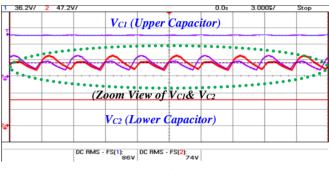

structure of  $S^3CM$  has twelve switches but the proposed CSCMLI topology requires eleven switches which further reduces the logic gates of pulse generation signal, driver circuits and increases the overall power density. In order to generate the nine-level stepped output voltage level the switching sequence of each level is given in Table.1. Here, nine-level inverter is discussed and it has zero to four state of operation in positive and negative cycle. Initially, the capacitors  $(C_1 \& C_2)$  are charged to  $V_{in}/2$  in state 1 and 2, the output voltage levels are  $\pm V_{in}/2$  &  $\pm V_{in}$ . In state 3 and 4, the stored the capacitor voltages are discharged to load and the load values are  $\pm 3V_{in}/2$  &  $\pm 2V_{in}$  as illustrated in Fig.2 (a)-(e). In this way, the voltages are boosted by charging and discharging of capacitors. The charging and discharging of capacitors are done equally to balance the voltages. The upper capacitor value is higher than the lower voltage capacitor in [10], but here both the capacitors have equal values because the charging and discharging period is equal.

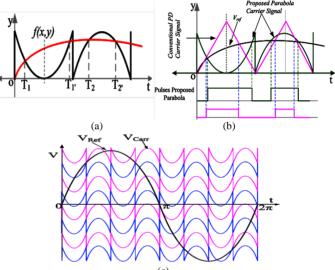

Fig. 3(a) proposed parabola carrier signal (b) conventional and proposed carrier signals with pulse width variations and (c) Level shifted proposed parabola carrier signal technique

To improve the output voltage rms and to minimize the voltage harmonics a new carrier signal PWM scheme is presented in this section. The proposed modulation strategy falls under the level shift modulation techniques (LS-PWM). conventional level shift modulation technique is classified into (i) phase disposition (PD), (ii) phase opposite disposition (POD) and (iii) alternate phase opposite disposition (APOD). The proposed carrier is applicable to all three categories. The sideband harmonics are higher in the traditional PWM technique and to minimize the sideband harmonics, the carrier frequency to be high. This causes high electromagnetic interference, which affects the converter and its operation. This section presents a modified carrier signal with variation of pulse widths as shown in Fig.3 (a) and (b). The "u-n" wave is basically parabolic in nature, hence the variable controlled waveform f(x,y) as

| TABLE 2 COMPARISON OF PROPOSED MAJE LEVEL BUJERTER MITH COMPANIES  | NIAL AND OTHER RECENT COMILETONIC OCIEC |

|--------------------------------------------------------------------|-----------------------------------------|

| TABLE. 2 COMPARISON OF PROPOSED NINE-LEVEL INVERTER WITH CONVENTIO | NAL AND OTHER RECENT SCIVILL TOPOLOGIES |

| Topologies | N <sub>Switches</sub> | N <sub>Source</sub> | N <sub>Capacitors</sub> | $V_{C,rating}$            | $N_{\text{Diode}}$ | $MBV_{p.u}$     | $TBV_{p.u}$        | Capacitor Balancing    | Voltage boosting Ability | Negative<br>Level   |    |              |

|------------|-----------------------|---------------------|-------------------------|---------------------------|--------------------|-----------------|--------------------|------------------------|--------------------------|---------------------|----|--------------|

| NPC        | 16                    | 1                   | 8                       | V <sub>in</sub> /4        | 56                 | 56              |                    |                        |                          | Additional Circuits | No | via last two |

|            | 10                    | •                   | Ŭ                       | 7 HV -                    |                    | V <sub>in</sub> | 16 V <sub>in</sub> | Required for >3-Level  | 110                      | arms                |    |              |

| FC 16      | 16                    | 16 1<br>16 4        | 31                      | V <sub>in</sub> /4        | -                  |                 |                    | No additional Circuits | No                       | via last two        |    |              |

|            | 10                    |                     | 31                      | <b>v</b> <sub>in</sub> /4 |                    |                 |                    | Required               |                          | arms                |    |              |

| СНВ        | 16                    |                     | -                       | -                         | -                  |                 |                    | Not Applicable         | -                        | via H-bridge        |    |              |

| [4]        | 12                    | 2                   | 2                       | Vin                       | 2                  | $2V_{in}$       | 20 V <sub>in</sub> | Calf Dalancina         |                          | via H-bridge        |    |              |

| [5]        | 8                     | 1                   | 3                       | $V_{in}$                  | 6                  | $4V_{in}$       | 20 V <sub>in</sub> |                        |                          | via H-bridge        |    |              |

| [6]        | 10                    | 1                   | 2                       | V <sub>in</sub>           | 1                  | $4V_{in}$       | 24 V <sub>in</sub> |                        |                          | inherent            |    |              |

| [7]        | 10                    | 2                   | 2                       | $V_{in}$                  | 4                  | $4V_{in}$       | 20 V <sub>in</sub> |                        | Yes                      | via H-bridge        |    |              |

| [8]        | 19                    | 1                   | 3                       | $V_{in}$                  | 1                  | V <sub>in</sub> | 19 V <sub>in</sub> | Self Balancing         | ies                      | inherent            |    |              |

| [9]        | 8                     | 1                   | 4                       | $2V_{in}$                 | 1                  | $2V_{in}$       | 16 V <sub>in</sub> |                        |                          | via H-bridge        |    |              |

| [11]       | 12                    | 1                   | 2                       | V <sub>in/</sub> 2        | 1                  | Vin             | 12 V <sub>in</sub> |                        |                          | inherent            |    |              |

| Proposed   | 11                    | 1                   | 2                       | V <sub>in</sub> /2        | 1                  | Vin             | 11 V <sub>in</sub> |                        |                          | inherent            |    |              |

\*MBV-Maximum Blocking Voltage on Individual Switches, TBV- Total Blocking Voltage of Switches

$$F(x,y) = \frac{A_{00}}{2} + \sum_{n=1}^{\infty} \left[ A_{0n} \cos ny + B_{0n} \sin ny \right] + \sum_{m=1}^{\infty} \left[ A_{0m} \cos mx + B_{0m} \sin mx \right] + \sum_{m=1}^{\infty} \sum_{m=-\infty}^{\infty} \left[ A_{mn} \cos (mx + ny) + B_{mn} \sin (mx + ny) \right]$$

$$(1)$$

where m is the carrier index variable and n is the baseband index variable. The above equation consists of fundamental component and baseband harmonics, carrier harmonics and sideband harmonics [12]. Since the u-n wave is parabolic in nature the f(x,y) function in the above equation can be replaced with  $x^2$  and the fundamental Fourier equation for voltage is

given as:

$$A_{00} + jB_{00} = \frac{2V_{dc}}{2\pi^2} \times \int_{-\pi}^{\pi} (1 + \pi M \cos y) dy$$

(2)

Where 'M' is modulation index. By solving (2), the fundamental value is  $A_{00} = 2V_{dc}$ ,  $B_{00} = 0$  when double edge modulation is used. Since the duty cycle of each pulse is higher than the conventional PWM and the conduction time is high in parabolic PWM technique as shown in Fig.3(b) and generalized level shifted carrier signal ( $V_{Carr}$ ) with sinusoidal reference signal ( $V_{Ref}$ ) is represented in Fig.3.(c). The comparison of proposed topology with other recent topologies is given in Table.2.

### III. SIMULATION AND EXPERIMENTAL RESULTS

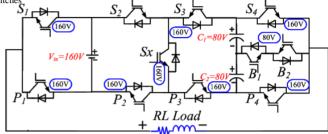

The simulation and experimental verification of *CSCMLI* is carried out by using MATLAB/Simulink and *DSpace-1104* for pulse generation and circuit diagram is depicted in Fig.4. The simulation and experimental parameters values are listed in Table. 3. In simulation the input voltage is 320V and the capacitor ratings are  $4700\mu F$  with voltage rating of 80V, these values are chosen based on the percentage of ripples in the capacitor voltage and switching frequency of the inverter.

TABLE. 3 PARAMETER USED IN SIMULATION AND EXPERIMENTAL

| SETUP                               |                          |                       |  |  |  |  |  |

|-------------------------------------|--------------------------|-----------------------|--|--|--|--|--|

| Parameters                          | Simulation               | Experimental          |  |  |  |  |  |

| DC Input voltage (V <sub>in</sub> ) | 320V                     | 320V                  |  |  |  |  |  |

| Capacitor Rating $(C_1,C_2)$        | 80V,4700μF               | 80V,4700μF            |  |  |  |  |  |

| R,L Load                            | $150\Omega,300\text{mH}$ | R-L load bank         |  |  |  |  |  |

| Output Voltage (Vout)               | $228V(V_{\text{rms}})$   | $228V(V_{rms})$       |  |  |  |  |  |

| Output Current (I <sub>o</sub> )    | $1.8A (I_{rms})$         | $0.5A-1.8A (I_{rms})$ |  |  |  |  |  |

| Output Power                        | 0.1kW-0.3kW              | 0.1kW- 0.4kW          |  |  |  |  |  |

| Switching Frequency                 | 50Hz, 2.5kHz             | 50Hz, 2.5kHz          |  |  |  |  |  |

| Voltage THD                         | 13.11%, 12.52%           | 13.95%, 13.1%         |  |  |  |  |  |

Fig.4 Simulated proposed nine level MLI with blocking voltage on the individual switches

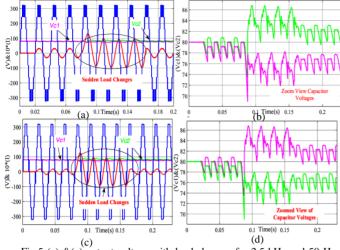

The proposed inverter along with the modulation technique is verified in both high switching frequency (2.5 kHz) and fundamental switching frequency (50Hz) in simulation and experimental model. The corresponding switches are triggered by using parabolic modulation technique and the simulated results are captured as shown in Fig.5. The dynamic performance is simulated by varying the resistive-inductive load values from high-low-high as shown in Fig.5 (a) and the capacitor voltages are shown in Fig.5 (b), i.e the capacitor is independent of the load power factor. For motor drive applications, the high switching frequency is not preferred, so the proposed topology and modulation scheme is verified for low switching frequency of 50 Hz and waveforms are shown in Fig.5(c) and (d). In experimental setup, the semikron IGBT SKM75GB063D IGBT and SKYPER-32-PRO-R gate driver circuits are used. The dead time of 2µs is provided by using RC network. The input voltage  $(V_{in})$  320V is given through the direct DC supply and a variable RL load banks of 0.1kW to 0.4kW is used.

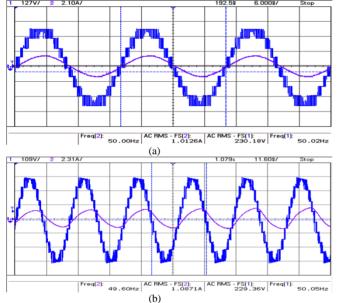

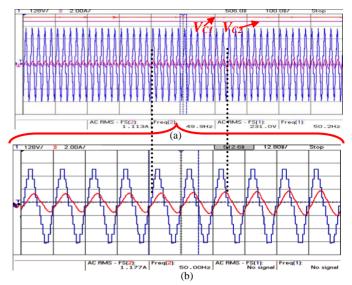

In the hardware, the high and low switching frequencies in PWM control with unity power factor are tested and waveforms are shown Fig. 6(a) and Fig.7 (a). The dynamic performance of proposed control and the inverter is explored in both high and low switching frequencies and the corresponding output voltage and current waveforms are shown in Fig.6 (b) and Fig.7(b). For dynamic performance the load values are gradually varied from high to low. For lagging power factor, the corresponding capacitor voltage waveform is shown in Fig.7(c). It is confirming that the proposed topology and parabola modulation technique is able to adopt for load variations. Further, the voltage THD value of proposed modulation technique is 12.52% and 13.1% for high and low switching frequency, respectively which is slightly lower than the other conventional PWM methods.

Fig.5 (a) &(c) output voltage with load changes for 2.5 kHz and 50 Hz switching frequency, (b) & (d) the capacitor voltage during load changes

Fig.6 Experimental results of proposed nine level inverter with switching frequency of 2.5 kHz (a) static load with high load resistance value (b) varying load with high load inductance value

The sizing of capacitor is

$$C_1 = C_2 = \frac{I_{pk}}{\Delta V_C \times f_{sw}} \tag{3}$$

In (3), voltage ripples ( $\Delta V_C$ ), switching frequency ( $f_{sw}$ ), and the peak load current ( $I_{pk}$ ) are chosen and the captured voltage waveforms are shown in Fig.7(c). Further to investigate the performance of modulation technique, the rms voltage and THDs are measured for various modulation indices and is listed in Table.4.

TABLE.4 THD COMPARISON OF VARIOUS MODULATION TECHNIQUES FOR SWITCHING FREQUENCY OF 2.5 KHZ

| Modulation<br>Techniques |           | Ma=1.0    |       | Ma=0.8    |       | Ma=0.6           |       | _    |  |

|--------------------------|-----------|-----------|-------|-----------|-------|------------------|-------|------|--|

|                          |           | $V_{rms}$ | THD%  | $V_{rms}$ | THD%  | $V_{\text{rms}}$ | THD%  | [1   |  |

| Sawtooth PWM             |           | 225.8     | 14.32 | 188.2     | 17.24 | 143.8            | 25.44 | _    |  |

| Sinusoidal<br>PWM        | PD        | 226.7     | 13.66 | 189.5     | 16.99 | 145.3            | 24.36 | -    |  |

|                          | POD       | 226.4     | 13.46 | 189.7     | 16.81 | 145.3            | 24.30 | _ [2 |  |

|                          | APOD      | 226.5     | 13.78 | 189.7     | 16.90 | 145.3            | 24.12 |      |  |

|                          | Parabolic | 228.4     | 12.52 | 189.3     | 15.66 | 146.0            | 22.61 |      |  |

Fig.7 Experimental results for 2.5 kHz switching frequency (a) voltage and current for continuous load changes (b) zoomed view and (c) voltage across the capacitors  $C_1 \& C_2$

**CONCLUSION**

IV.

A new voltage boost with self-voltage balancing across the capacitor in the nine level CSCMLI topology is proposed along with a new modified carrier signal. A single dc source is used and the output voltage is boosted twice i.e voltage gain is doubled. The voltage across each switch is limited to  $V_{\rm in}$  which is the remarkable advantage of the proposed topology, because the number of active switches are reduced and this leads to low power losses. The capacitors voltages are not affected due to the load variations i.e capacitor voltages are independent of load power factor. Further, the proposed modulation technique is adaptable for both low and high switching frequency applications like a renewable energy power conversion system, AC drive applications, etc.

## ACKNOWLEDGEMENT

This project is supported by SRM institute of Science and Technology Under the scheme of Selective Excellence Initiative: SRM/R/AR (A)/2015/126/866.

#### REFERENCES

- X. Liang and C. Andalib-Bin-Karim, "Harmonics and Mitigation Techniques through Advanced Control in Grid-Connected Renewable Energy Sources: A Review," *IEEE Trans. on Ind. Appl.*, vol. 54, no. 4, pp. 3100-3111, July-Aug. 2018.

- M.A Jagabar Sathik and K. Vijayakumar, "An assessment of recent multilevel inverter topologies with reduced power electronics components for renewable applications," *Renewable and Sustainable Energy Reviews*, vol.82, no.3, pp.3379-3399, Feb-2018.

- [3]. L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A.M. Prats, "The age of multilevel converters arrives," *IEEE Ind. Electron.Mag.*, vol. 2, no. 2, pp. 28–39, Jun. 2008.

- [4]. J. Liu, K. W. E. Cheng and Y. Ye, "A Cascaded Multilevel Inverter Based on Switched-Capacitor for High-Frequency AC Power Distribution System," in *IEEE Transactions on Power Electronics*, vol. 29, no. 8, pp. 4219-4230, Aug. 2014.

- [5]. Y. Ye, K. W. E. Cheng, J. Liu and K. Ding, "A Step-Up Switched-Capacitor Multilevel Inverter With Self-Voltage Balancing," in *IEEE Transactions on Industrial Electronics*, vol. 61, no. 12, pp. 6672-6680, Dec. 2014.

- [6]. R. Barzegarkhoo, M. Moradzadeh, E. Zamiri, H. Madadi Kojabadi and F. Blaabjerg, "A New Boost Switched-Capacitor Multilevel Converter With Reduced Circuit Devices," in *IEEE Transactions on Power* Electronics, vol. 33, no. 8, pp. 6738-6754, Aug. 2018.

- [7]. R. Shalchi Alishah, S. H. Hosseini, E. Babaei, M. Sabahi and G. B. Gharehpetian, "New High Step-Up Multilevel Converter Topology With Self-Voltage Balancing Ability and Its Optimization Analysis," in *IEEE Transactions on Industrial Electronics*, vol. 64, no. 9, pp. 7060-7070, Sept. 2017.

- [8]. A. Taghvaie, J. Adabi and M. Rezanejad, "A Self-Balanced Step-Up Multilevel Inverter Based on Switched-Capacitor Structure," in *IEEE Transactions on Power Electronics*, vol. 33, no. 1, pp. 199-209, Jan. 2018.

- [9]. M. Saeedian, M. E. Adabi Firouzjaee, S. M. Hosseini, J. Adabi and E. Pouresmaeil, "A Novel Step-Up Single Source Multilevel Inverter: Topology, Operating Principle and Modulation," in *IEEE Transactions on Power Electronics*.doi: 10.1109/TPEL.2018.2848359

- [10]. J. Liu, J. Wu and J. Zeng, "Symmetric/Asymmetric Hybrid Multilevel Inverters Integrating Switched-Capacitor Techniques," in *IEEE Journal* of Emerging and Selected Topics in Power Electronics. doi: 10.1109/JESTPE.2018.2848675

- [11]. S. Lee, "Single-Stage Switched-Capacitor Module (S<sup>3</sup>CM) Topology for Cascaded Multilevel Inverter," in *IEEE Transactions on Power Electronics*. doi: 10.1109/TPEL.2018.2805685.

- [12]. D. G. Holmes and T. Lipo, Pulse Width Modulation for Power Converters: Principles and Practice. Piscataway, NJ: IEEE Press, 2003.